XILINX INC.

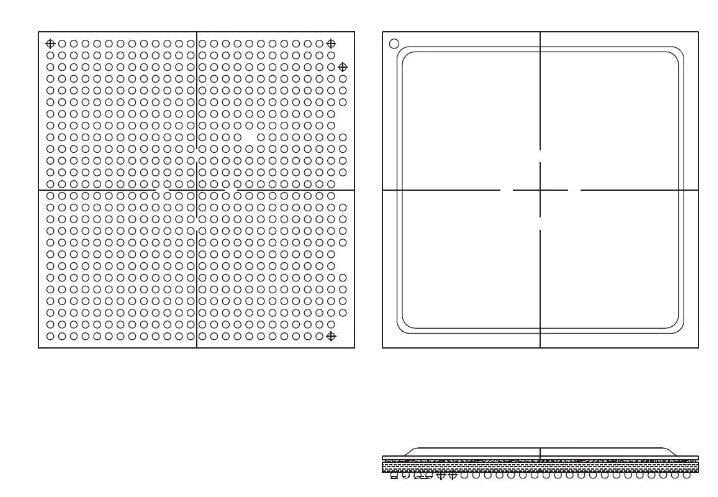

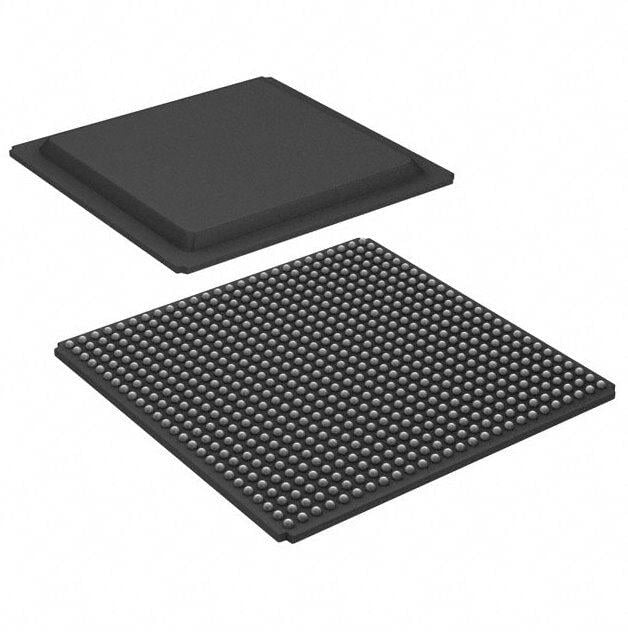

Xilinx Field Programmable Gate Array, Part #: XC5VFX30T-1FFG665C | FPGA | DEX

Xilinx Field Programmable Gate Array, Part #: XC5VFX30T-1FFG665C | FPGA | DEX

Couldn't load pickup availability

Xilinx Field Programmable Gate Array, Part #: XC5VFX30T-1FFG665C contains many hard-IP system level blocks, including powerful 36-Kbit block RAM/FIFOs, second generation 25 x 18 DSP slices, SelectIO™ technology with built-in digitally-controlled impedance, ChipSync™ source-synchronous interface blocks, system monitor functionality, enhanced clock management tiles with integrated DCM (Digital Clock Managers) and phase-locked-loop (PLL) clock generators, and advanced configuration options. Additional platform dependant features include power-optimized high-speed serial transceiver blocks for enhanced serial connectivity, PCI Express® compliant integrated Endpoint blocks, tri-mode Ethernet MACs (Media Access Controllers), and high-performance PowerPC® 440 microprocessor embedded blocks. These features allow advanced logic designers to build the highest levels of performance and functionality into their FPGA-based systems. Built on a 65-nm state-of-the-art copper process technology, Virtex-5 FPGAs are a programmable alternative to custom ASIC technology. Most advanced system designs require the programmable strength of FPGAs. Virtex-5 FPGAs offer the best solution for addressing the needs of high-performance logic designers, high-performance DSP designers, and high-performance embedded systems designers with unprecedented logic, DSP, hard/soft microprocessor, and connectivity capabilities. The Virtex-5 LXT, SXT, TXT, and FXT platforms include advanced high-speed serial connectivity and link/transaction layer capability.

Features

• Five platforms LX, LXT, SXT, TXT, and FXT

• Cross-platform compatibility

• Most advanced, high-performance, optimal-utilization, FPGA fabric

• Powerful clock management tile (CMT) clocking

• 36-Kbit block RAM/FIFOs

• High-performance parallel SelectIO technology

XLX:XC5VFX30T-1FFG665C

XC5VFX30T-1FFG665C