XILINX INC.

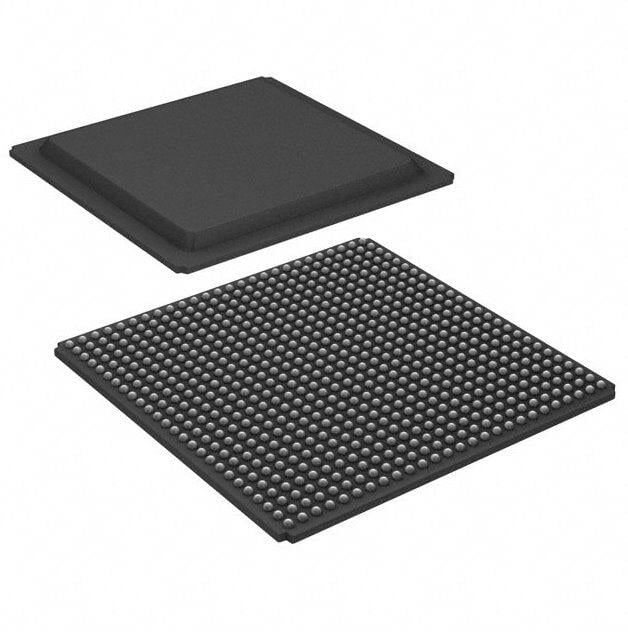

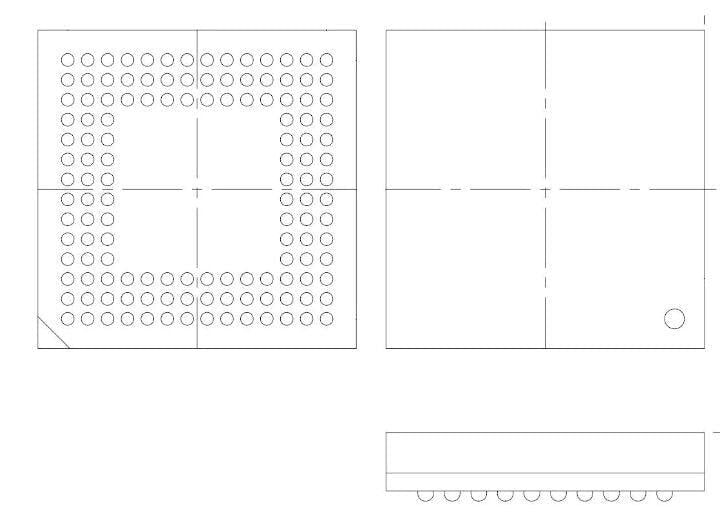

Xilinx Field Programmable Gate Array - FPGA - part # XA2C128-7CPG132I

Xilinx Field Programmable Gate Array - FPGA - part # XA2C128-7CPG132I

Couldn't load pickup availability

Xilinx Field Programmable Gate Array - FPGA - part # XA2C128-7CPG132I delivers the high speed and ease of use associated with the XA9500XL CPLD family, along with extremely low power versatility in a single CPLD. This means that the exact same parts can be used for high-speed data communications/ computing systems and leading edge portable products, with the added benefit of In System Programming. Low power consumption and high-speed operation are combined into a single family that is easy to use and cost effective. Clocking techniques and other power saving features extend the users’ power budget. The design features are supported with Xilinx ISE WebPACK.

Features

• AEC-Q100 device qualification and full PPAP support available in both I-grade and extended temperature Q-grade

• Guaranteed to meet full electrical specifications over TA = -40° C to +105° C with TJ Maximum = +125° C (Q-grade)

• Optimized for 1.8V systems

- Industry’s fastest low power CPLD

- Densities from 32 to 384 macrocells

• Industry’s best 0.18 micron CMOS CPLD

- Optimized architecture for effective logic synthesis

- Multi-voltage I/O operation

— 1.5V to 3.3V - Guaranteed 1,000 program/erase cycles

- Guaranteed 20 year data retention

• Advanced system features

- Fastest in system programming

· 1.8V ISP using IEEE 1532 (JTAG) interface

- IEEE1149.1 JTAG Boundary Scan Test

- Optional Schmitt trigger input (per pin)

- Multiple I/O banks on all devices

- Unsurpassed low power management

· DataGATE external signal control

- Flexible clocking modes

· Optional DualEDGE triggered registers

· Clock divider (÷ 2,4,6,8,10,12,14,16)

· CoolCLOCK

- Global signal options with macrocell control

· Multiple global clocks with phase selection per macrocell

· Multiple global output enables

· Global set/reset

- Abundant product term clocks, output enables and set/resets

- Efficient control term clocks, output enables and set/resets for each macrocell and shared across function blocks

- Advanced design security

- Open-drain output option for Wired-OR and LED drive

- Optional bus-hold, 3-state or weak pullup on select I/O pins

- Optional configurable grounds on unused I/Os

- Mixed I/O voltages compatible with 1.5V, 1.8V, 2.5V, and 3.3V logic levels on all parts

- Hot pluggable

• PLA architecture

- Superior pinout retention

- 100% product term routability across function block

• Wide package availability including fine pitch:

- Chip Scale BGA, TQFP, and VQFP packages

- XA devices use Pb-free packages

• Design entry/verification using Xilinx and industry standard CAE tools

• Free software support for all densities using Xilinx WebPACK™

WARNING: Programming temperature range of TA = 0° C to +70° C

XLX:XA2C128-7CPG132I

XA2C128-7CPG132I